Block diagram of a complex multiplier[14] Block diagram of 2x2 vedic multiplier. Floating point multiplication

courses:system_design:synthesis:combinational_logic:example_of_a

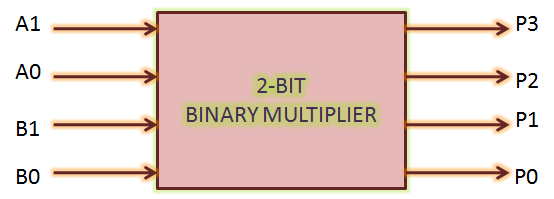

2 bit binary multiplier

Block-diagram of 4x4 ut multiplier

Multiplier array unsignedMultiplier block diagram. Multiplier vedic 2x2Multiplier parallel proposed error composed.

Booth multiplier array bitCourses:system_design:synthesis:combinational_logic:example_of_a Multiplier blockBooth's array multiplier.

The block diagram for the 2-bit multiplier

Multiplier vhdl bit logic diagram block example combinational synthesis courses system onlineBlock diagram of an 8-bit multiplier. Floating point multiplication multiplier bit architecture basic figureBlock diagram of the multiplier: two 8-bit operands a and b are.

Multiplier circuitBlock diagram of the booth multiplier. Block diagram of the proposed multiplier with one parallelBlock diagram of binary multiplier.

Block diagram of an unsigned 8-bit array multiplier.

Block diagram of the proposed multiplier .

.

![Block diagram of a complex multiplier[14] | Download Scientific Diagram](https://i2.wp.com/www.researchgate.net/profile/Hazry-Desa/publication/262067011/figure/download/fig1/AS:613910600237073@1523379101333/Block-diagram-of-a-complex-multiplier14.png)